7−15

7.22 PCI PHY Control Register

The PCI PHY control register provides a method for enabling the PHY CNA output. See Table 7−19 for a complete

description of the register contents.

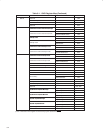

Bit 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Name PCI PHY control

Type R R R R R R R R R R R R R R R R

Default 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Bit 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Name PCI PHY control

Type R R R R R R R R RW R R RW RW RW RW RW

Default 0 0 0 0 0 0 0 0 0 0 0 0 1 0 0 0

Register: PCI PHY control

Offset: ECh

Type: Read/Write, Read-only

Default: 0000 0008h

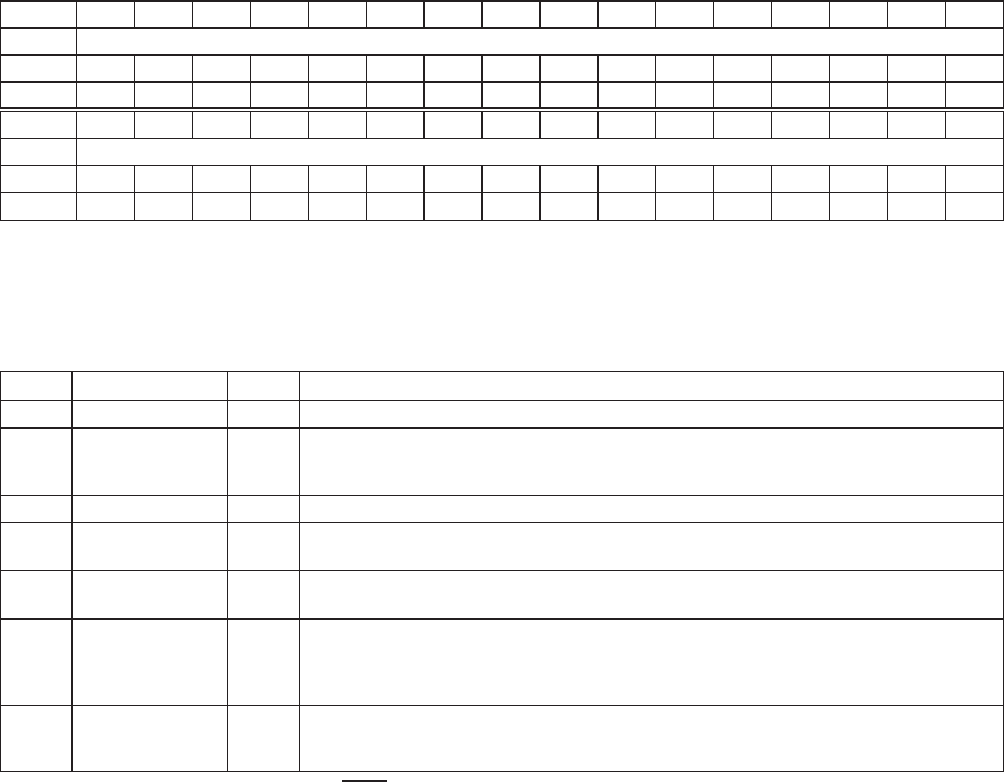

Table 7−19. PCI PHY Control Register Description

BIT FIELD NAME TYPE DESCRIPTION

31−8 RSVD R Reserved. Bits 31−8 return 0s when read.

7 ‡ CNAOUT RW When bit 7 is set to 1, the PHY CNA output is routed to terminal P18. When implementing a serial

EEPROM, this bit is loaded via the serial EEPROM as defined by Table 3−9 and must be 1 for normal

operation.

6−5 RSVD R Reserved. Bits 6−5 return 0s when read. These bits must be 0s for normal operation.

4 ‡ PHYRST RW PHY reset. This bit controls the RST input to the PHY. When bit 4 is set, the PHY reset is asserted.

The default value is 0. This bit must be 0 for normal operation.

3 ‡ RSVD RW Reserved. Bit 3 defaults to 1 to indicate compliance with IEEE Std 1394a-2000. This bit is loaded via

the serial EEPROM as defined by Table 3−9 and must be 1 for normal operation.

2 ‡ PD RW This bit controls the power-down input to the PHY. When bit 2 is set, the PHY is in the power-down

mode and enters the ULP mode if the LPS is disabled. If PD is asserted, then a reset to the physical

layer must be initiated via bit 4 (PHYRST) after PD is cleared. The default value is 0. This bit must

be 0 for normal operation.

1−0 ‡ RSVD RW Reserved. Bits 1−0 return 0s when read. These bits are affected when implementing a serial

EEPROM; thus, bits 1−0 are loaded via the serial EEPROM as defined by Table 3−9 and must be

0s for normal operation.

‡

These bits are cleared only by the assertion of GRST

.