Interface Circuit

2-4

Specifications

2.2 Interface Circuit

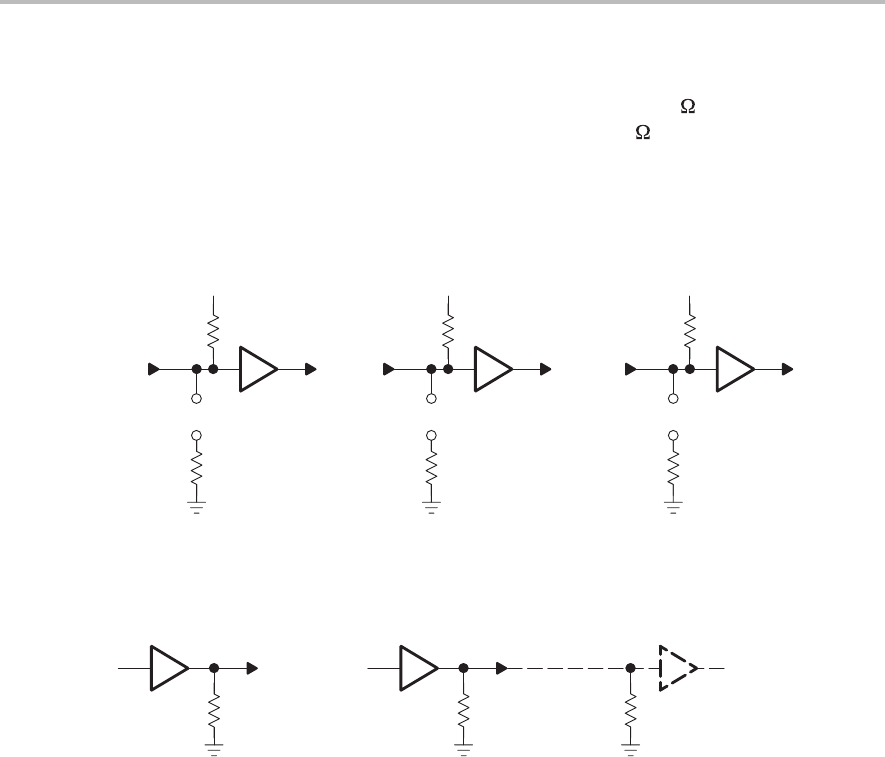

The input interface circuit of VD, HD, and MCK shown in Figure 2–1, consists

of one SN75124 input gate pulled up through a 4.7-k resistor to 5 Vdc and

pulled down to ground through an optional 100- resistor. The optional pull

down is selected by jumpers JP1 (MCK), JP2 (HD), and JP3 (VD).

Figure 2–1. Input Interface Circuit of VD, HD, and MCK

5 V

VD

4.7 kΩ

75124

JP3

100 Ω

GND

5 V

HD

4.7 kΩ

75124

JP2

100 Ω

GND

5 V

MCK

4.7 kΩ

75124

JP1

100 Ω

GND

Figure 2–2. Output Interface Circuit of Pixel and Shutter Monitor

75123

470 Ω

Shutter

Monitor

Pixel Out

100 Ω

470 Ω

(see Note A)

NOTE A. For pixel clock receiving, pull domain resistor 100 Ω is recommended.