Unibrain Fire-i 501/511/601/701/702/810 Operation Manual Page 65

0xF2F10018

Mode control register

Bit 31 : auto sync enable

Bit 30 : SIO enable mode (0 : custom mode, 1 : IIDC v1.31)

Bit 27 : auto sync complete (read only. 1: ready, 0: not yet auto-sync)

Read/Write

0xF2F1001C

1394 time stamp register(msb:bit0)

We recommend using native CYCLE_TIME register in Chap. 5.7.

Read only

0xF2F10100

Power on reset condition control register

Not Recommended

Please refer to IIDC v1.31 memory save/load channel.

Read/Write

(Self

Cleared)

0xF2F10104

Trigger control register

Not Recommended

Please refer to IIDC v1.31 trigger control register (address: 0xF0F00830)

Read/Write

0xF2F10108

Software trigger

Not Recommended

Please refer to IIDC v1.31 software trigger register (address: 0xF0F0062C)

Read only

0xF2F1010C

Strobe control register. Only supports active high polarity.

Not Recommended Please refer to IIDC v1.31strobe control register (address:

0xF0F0048C -> 0xF2F23200)

Read/Write

0xF2F10110

Trigger noise filter register (External trigger only)

Bit 22~Bit 31 : trigger masking range (M, unit : usec, range:0~ 999)

Read/Write

0xF2F10114

Multi-cut exposure & interval time control (for Mode 14)

Bit 16 ~ 31 : exposure time (E)

Bit 0 ~ 15 : exposure time interval (P)

Read/Write

0xF2F10184

Local ISO_EN control register for one-shot/multi-shot

Bit 31 : iso_enable ( 1: enable. 0: disable)

0xF2F1011C

Power on default memory channel

Bit 0 ~ Bit 3 : power on initial memory channel

Read/Write

0xF2F10200

Camera version register

Bit 16~Bit 31 : camera version

(ex: If reading value: 0x00003000, camera version is 3.000)

Read only

0xF2F10120

Bright Level for Iris Control Application

Bit 24 ~ Bit 31 : Bright Level for Image Capture

Read only

0xF2F10124

Test Pattern

Bit 0 : Vertical Grey Bar

Bit 1: Bias Grey Bar

Read/Write

0xF2F10158

Trigger mode 12/13 Gain/Shutter Control register

Bit 0 : Presence inquiry (read only)

Bit 5 : Setting complete (self cleared)

Bit 6 : Gain/Shutter table setting enable for trigger mode 12/13

Read/Write

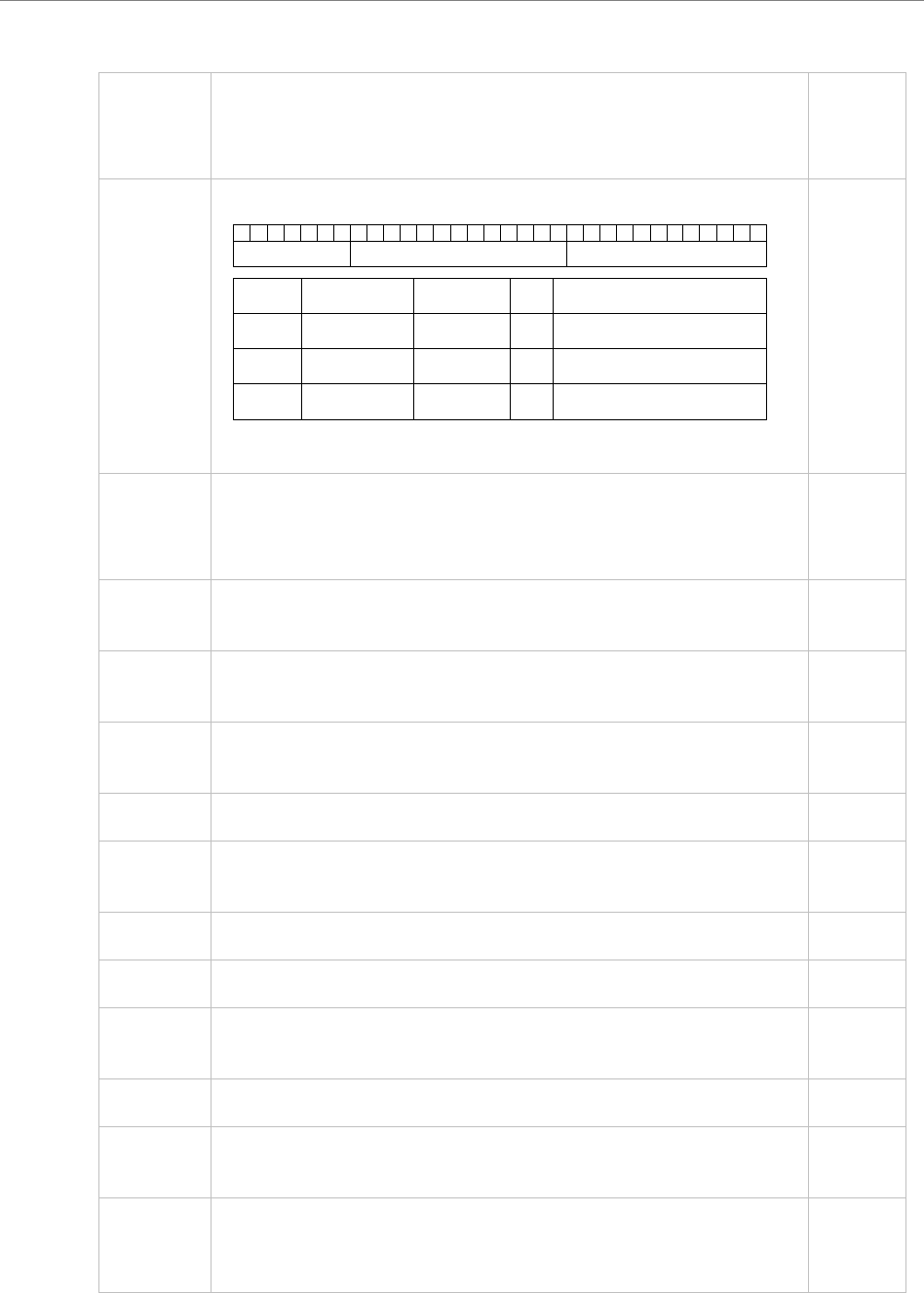

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

SECONDS COUNT CYCLE COUNT CYCLE OFFSET

Bit Numbe r Bit Name Function DIR Description

0 - 6

7 - 19

20 - 31

SECONDS COUNT

CYCLE COUNT

CYCLE OFFSET

Seconds Coun t

Cycle Coun t

Cycle Offset

R/W

R/W

R/W

1 Hz cycle timer counte r

8,000 Hz c ycle timer counte r

24.576 MHz c ycle timer counte r