Page 26

TM-2016-8 and TM-2016-8CL Progressive Scan Shutter Camera

Operation

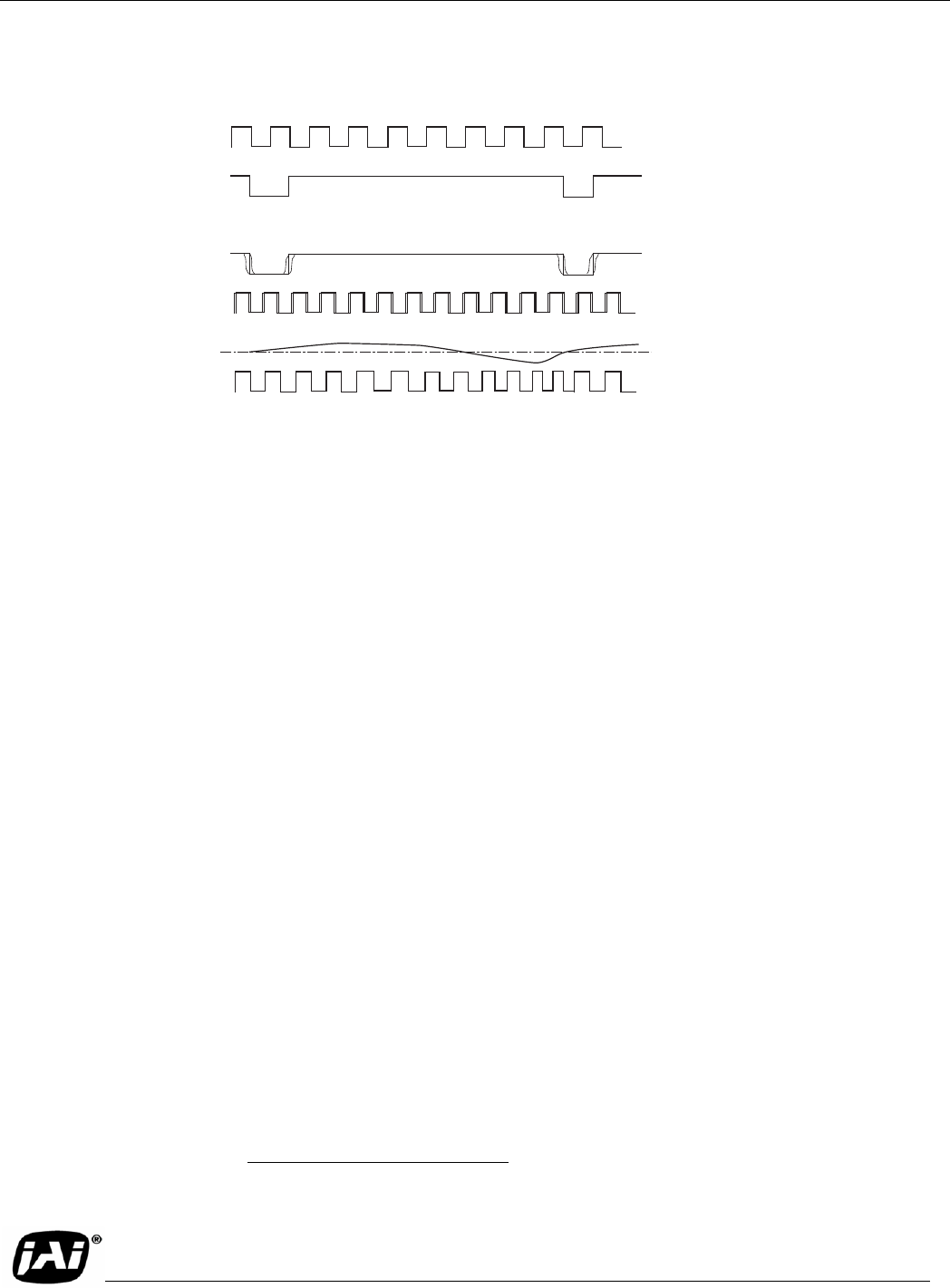

3.10.1 Pixel Clock Locking (optional)

*

For multiple-camera applications such as 2D or 3D measurement, multiple-camera inspection, a parallel

digital data input capability is important. The high resolution and precision measurement requires that

camera data be consistent with each other and free from PLL jitter. This is especially important for

digital output multiplexing. The TM-2016-8 has an optional capability for pixel clock locking. It takes

RS-644 (differential) external clock and H and V reset sync (TTL or RS-644). By doing this, each

camera’s digital data is in-phase with the pixel clock (data clock) for multiplexing or parallel input to a

frame grabber.

3.11 Serial Communication Kit (TM-2016-8)

The TM-2016-8’s functions can be controlled by a PC via RS-232C communication using the CS-232E

serial communication kit. This kit consists of the RS-232B-12 cable, software disk, and quick-start card.

The software disk contains setup files for the graphical user interface (GUI) program. Refer to the

software manual for information on the GUI.

*. Pixel clock locking option not available at time of publishing. Please check with JAI, Inc. for option

availability.

PLL jitter

VCO voltage swing

External Clock

External HD

Internal HD with PLL

Pixel clock

Pixel clock