Version 1.08 (04/07)Manual: CMOS Industrial Camera LOGLUX

i5

Page 32 of 46KAMERA WERK DRESDEN GmbH

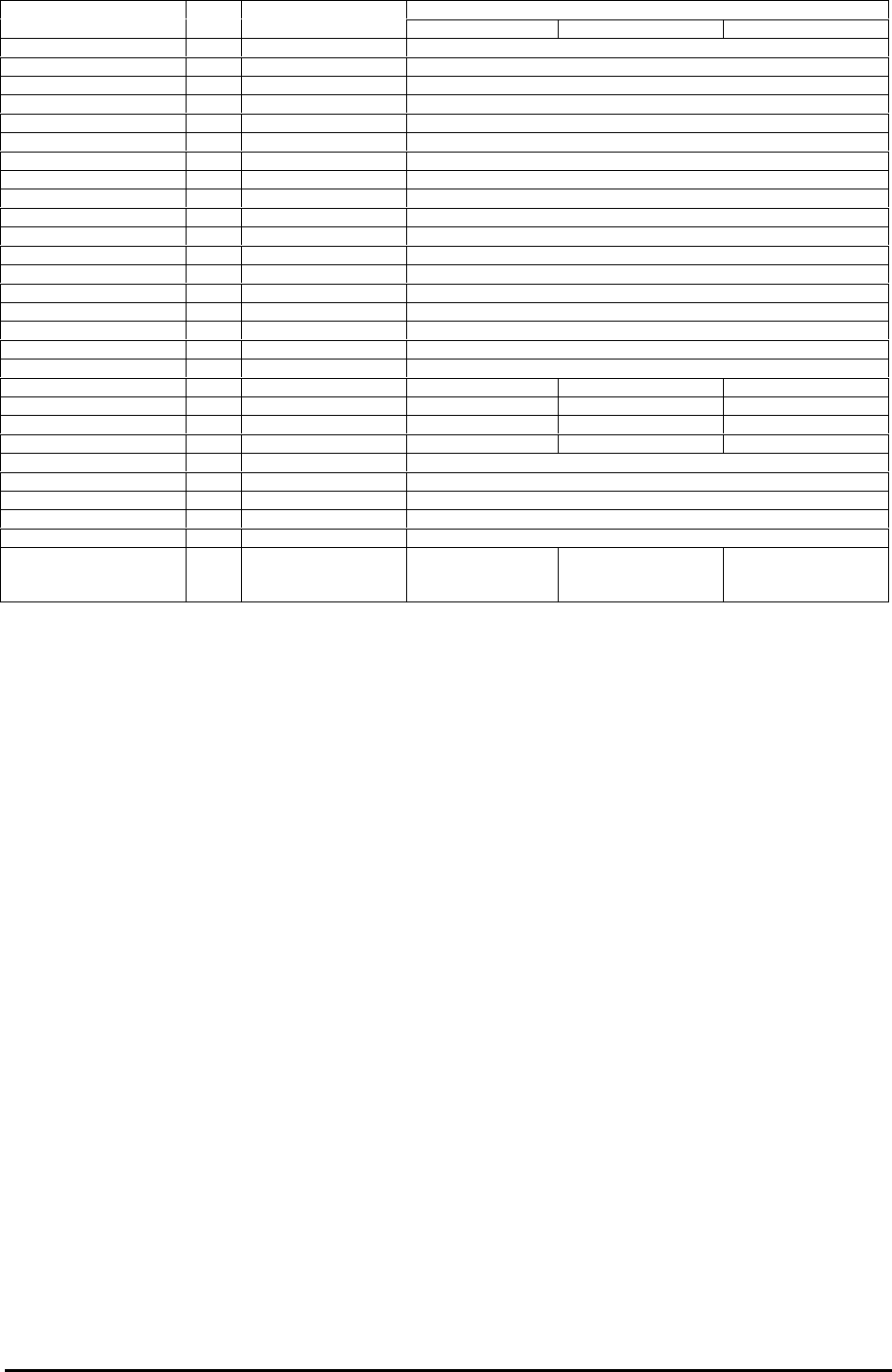

Initial profile value

RegisterAddr.Description

$x1$x2$x3

PROFILE_PIXELCLK$102Pixel clock rate4

.

10

7

PROFILE_TRGSOURCE$103Trigger source4 (free running trigger)

PROFILE_TRGDELAY$104Trigger delay0 (0 ns)

PROFILE_TRGRATE$108Trigger rate10 Hz

PROFILE_SMODE$10ASnapshot mode0 (sequence mode)

PROFILE_TMMODE$10CLook-up table (LUT)$0000 (no LUT)

PROFILE_SW0SOURCE

$10ESource, switchport 00 (off)

PROFILE_SW0POL$10FPolarity, switchport 01 (high active)

PROFILE_SW0DELAY$110Delay, switchport 00 (0 ns)

PROFILE_SW0LEN$114Sig. time, switchport 01000 (1 us)

PROFILE_SW1SOURCE

$118Source, switchport 00 (off)

PROFILE_SW1POL$119Polarity, switchport 01 (high active)

PROFILE_SW1DELAY$11ADelay, switchport 00 (0 ns)

PROFILE_SW1LEN$11ESig.time, switchport 01000 (1 us)

PROFILE_XSTART$130ROI X start position0

PROFILE_YSTART$132ROI Y start position0

PROFILE_WIDTH$134ROI width1278

PROFILE_HEIGHT$136ROI height1023

PROFILE_INT0$138Integration time slope 1003

.

10

7

PROFILE_INT1$13CIntegration time slope 2009

.

10

5

PROFILE_INT2$140Integration time slope 302

.

10

7

9

.

10

4

PROFILE_INT3$144Integration time l slope23

.

10

6

3

.

10

6

41

.

10

2

PROFILE_SHUTTER$148Shutter principle0 (synchronous shutter)

PROFILE_SUBSAMPL$149X/Y subsampling0 (no subsampling)

PROFILE_AMPLIFIER$14AAmplification factor0 (V=1.00)

PROFILE_CALIB$14BCalibration0 = fast calibration

PROFILE_PRCHARGE$14CPrecharge0 = precharge line

PROFILE_DESCRPTN$150

...

$16F

Profile descriptionSingle Integration

Slope

Dual Integration SlopeQuadruple Integration

Slope

Table 5 : List of register initial values of function group 'camera configuration'

PROFILE_PIXELCLKThe register specifies the frequency of the pixel clock in Hz. The pixel clock

has an influence on a number of parameters, among them the image readout

rate, and may lead to undesired effects, e.g. the fading of the last pixel read

out, if unfavorably set.

Example: w $102 #20000000;Pixel clock rate is 20 MHz

PROFILE_TRGSOURCE

The register describes the trigger source and the type of triggering. A single

snapshot, snapshot sequence or continuous "snapshot" can be triggered by

an external trigger signal, by signal CC1 (camera control 1) applied to the

CameraLink interface, or by setting bit 0 (corresponds to a register value of

1) in the PARAM_TRIGGER register. This releases a clock generator which

generates the trigger signals for the sensor at the desired frequency and in the

desired number. In the case of autonomous camera systems which are not

externally triggered, the camera can trigger itself during booting.

Example: w $103 #3;Trigger via TRegister

PROFILE_TRGDELAY

The register specifies a delay of the trigger event in nanoseconds. The actual

delay time is rounded to comply with the pixel clock accuracy (e.g.

TRGDELAY = 80 ⇒ 75.76ns delay at 66 MHz pixel clock rate ). There is also

a hardware-dependent delay in addition to the set delay time. Among others,

this hardware-dependent delay is determined by the camera-internal electrical

isolation of an optical coupling device (transmission time) or by the slope

(edge steepness) of the 24V trigger signal.

Example: w $104 #1000;delay is 1us