2-16 Computer Group Literature Center Web Site

Programming Details

2

PCI0 bus at 133MHz and the secondary PMCspan bus at 33 or 66 MHz.

See the PLX PCI6520 Specification for further programming information.

MV64360 Interrupt Controller

The MVME6100 uses the MV64360 interrupt controller to route internal

and external interrupt requests to the CPU and the PCI bus. The MV64360

interrupt controller registers are implemented as part of the CPU interface

unit in order to have minimum read latency from CPU interrupt handler.

This is not backward compatible with the Discovery I implementation

since the registers are placed at different offsets. The external interrupt

sources will use the GPP interface to register external interrupts. The

following table shows the MVME6100 interrupt assignment to MV64360

GPP pins.

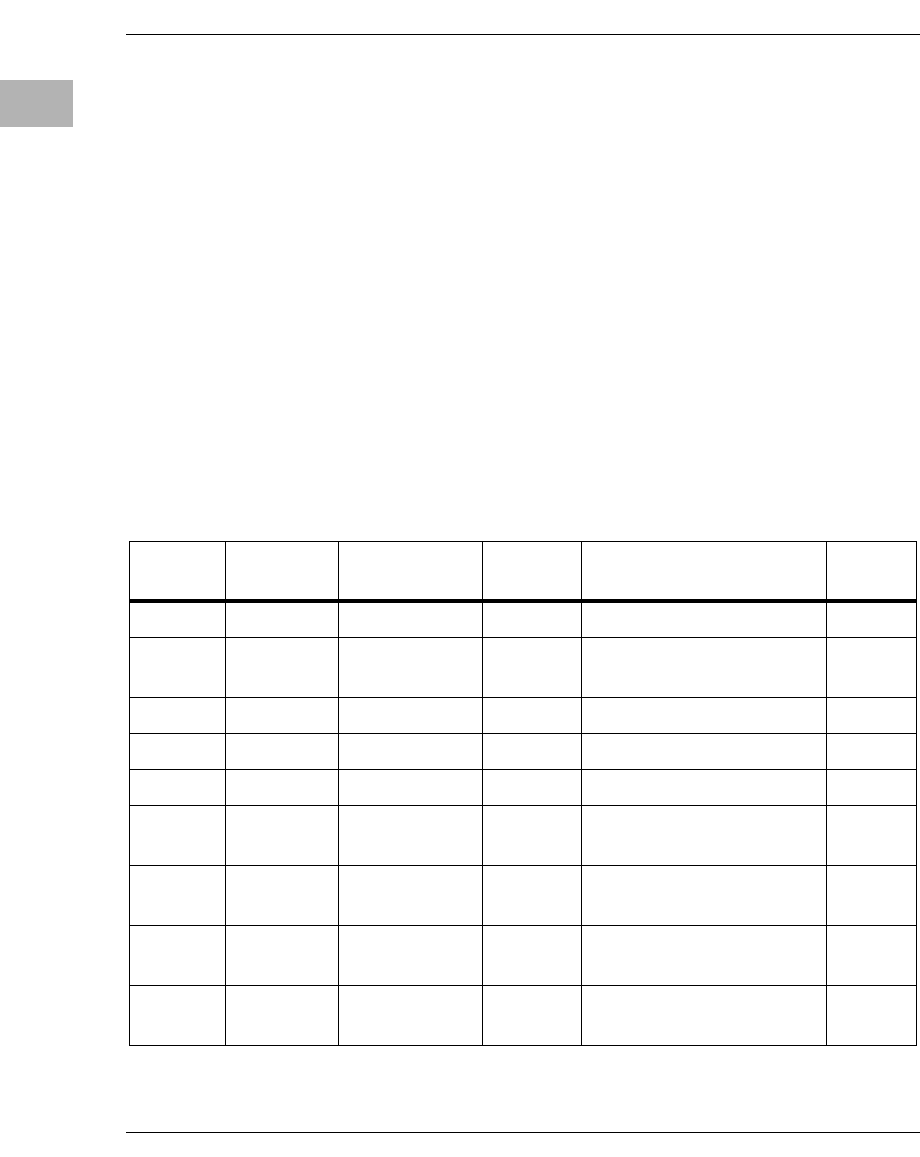

Table 2-8. MV64360 Interrupt Assignments

GPP

Group MV64360 Edge/Level Polarity Interrupt Source Notes

0 GPP[0] Level High COM1 || COM2 3

GPP[1] Level N.A. Unused, pulled high

onboard

7

GPP[2] Level Low ABORT#

GPP[3] Level Low RTC || Thermostat output 6

GPP[5] Level High IPMC761 interrupt 2

GPP[6] Level Low MV64360 WDNMI#

interrupt

GPP[7] Level Low BCM5421S PHY 1 INTR# ||

BCM5421S PHY 2 INTR#

2 GPP[16] Level Low PCI-PMC 0 INTA#, PMC 1

INTC#

2

GPP[17] Level Low PCI-PMC 0 INTB#, PMC 1

INTD#,

2