8−7

8.5 CSR Compare Register

The CSR compare register accesses the bus management CSR registers from the host through compare-swap

operations. This register contains the data to be compared with the existing value of the CSR resource.

Bit 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Name CSR compare

Type R R R R R R R R R R R R R R R R

Default X X X X X X X X X X X X X X X X

Bit 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Name CSR compare

Type R R R R R R R R R R R R R R R R

Default X X X X X X X X X X X X X X X X

Register: CSR compare

Offset: 10h

Type: Read-only

Default: XXXX XXXXh

8.6 CSR Control Register

The CSR control register accesses the bus management CSR registers from the host through compare-swap

operations. This register controls the compare-swap operation and selects the CSR resource. See Table 8−5 for a

complete description of the register contents.

Bit 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Name CSR control

Type RU R R R R R R R R R R R R R R R

Default 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Bit 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Name CSR control

Type R R R R R R R R R R R R R R RW RW

Default 0 0 0 0 0 0 0 0 0 0 0 0 0 0 X X

Register: CSR control

Offset: 14h

Type: Read/Write, Read/Update, Read-only

Default: 8000 000Xh

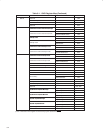

Table 8−5. CSR Control Register Description

BIT FIELD NAME TYPE DESCRIPTION

31 csrDone RU Bit 31 is set to 1 by the PCI7x21/PCI7x11 controller when a compare-swap operation is complete. It

is cleared whenever this register is written.

30−2 RSVD R Reserved. Bits 30−2 return 0s when read.

1−0 csrSel RW This field selects the CSR resource as follows:

00 = BUS_MANAGER_ID

01 = BANDWIDTH_AVAILABLE

10 = CHANNELS_AVAILABLE_HI

11 = CHANNELS_AVAILABLE_LO