3−23

3.8.5 16-Bit PC Card Power Management

The COE bit (bit 7) of the ExCA power control register (ExCA offset 02h/42h/802h, see Section 5.3) and PWRDWN

bit (bit 0) of the ExCA global control register (ExCA offset 1Eh/5Eh/81Eh, see Section 5.20) are provided for 16-bit

PC Card power management. The COE bit places the card interface in a high-impedance state to save power. The

power savings when using this feature are minimal. The COE bit resets the PC Card when used, and the PWRDWN

bit does not. Furthermore, the PWRDWN bit is an automatic COE, that is, the PWRDWN performs the COE function

when there is no card activity.

NOTE: The 16-bit PC Card must implement the proper pullup resistors for the COE and

PWRDWN modes.

3.8.6 Suspend Mode

The SUSPEND signal, provided for backward compatibility, gates the PRST (PCI reset) signal and the GRST (global

reset) signal from the PCI7x21/PCI7x11 controller. Besides gating PRST

and GRST, SUSPEND also gates PCLK

inside the PCI7x21/PCI7x11 controller in order to minimize power consumption.

It should also be noted that asynchronous signals, such as card status change interrupts and RI_OUT

, can be passed

to the host system without a PCI clock. However, if card status change interrupts are routed over the serial interrupt

stream, then the PCI clock must be restarted in order to pass the interrupt, because neither the internal oscillator nor

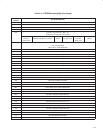

an external clock is routed to the serial-interrupt state machine. Figure 3−14 is a signal diagram of the suspend

function.

RESET

GNT

SUSPEND

PCLK

RESETIN

SUSPENDIN

PCLKIN

External Terminals

Internal Signals

Figure 3−14. Signal Diagram of Suspend Function

3.8.7 Requirements for Suspend Mode

The suspend mode prevents the clearing of all register contents on the assertion of reset (PRST or GRST) which

would require the reconfiguration of the PCI7x21/PCI7x11 controller by software. Asserting the SUSPEND

signal