Epson Research and Development Page 99

Vancouver Design Center

Hardware Functional Specification S1D13708

Issue Date: 02/03/07 X39A-A-001-02

1. Ts = pixel clock period

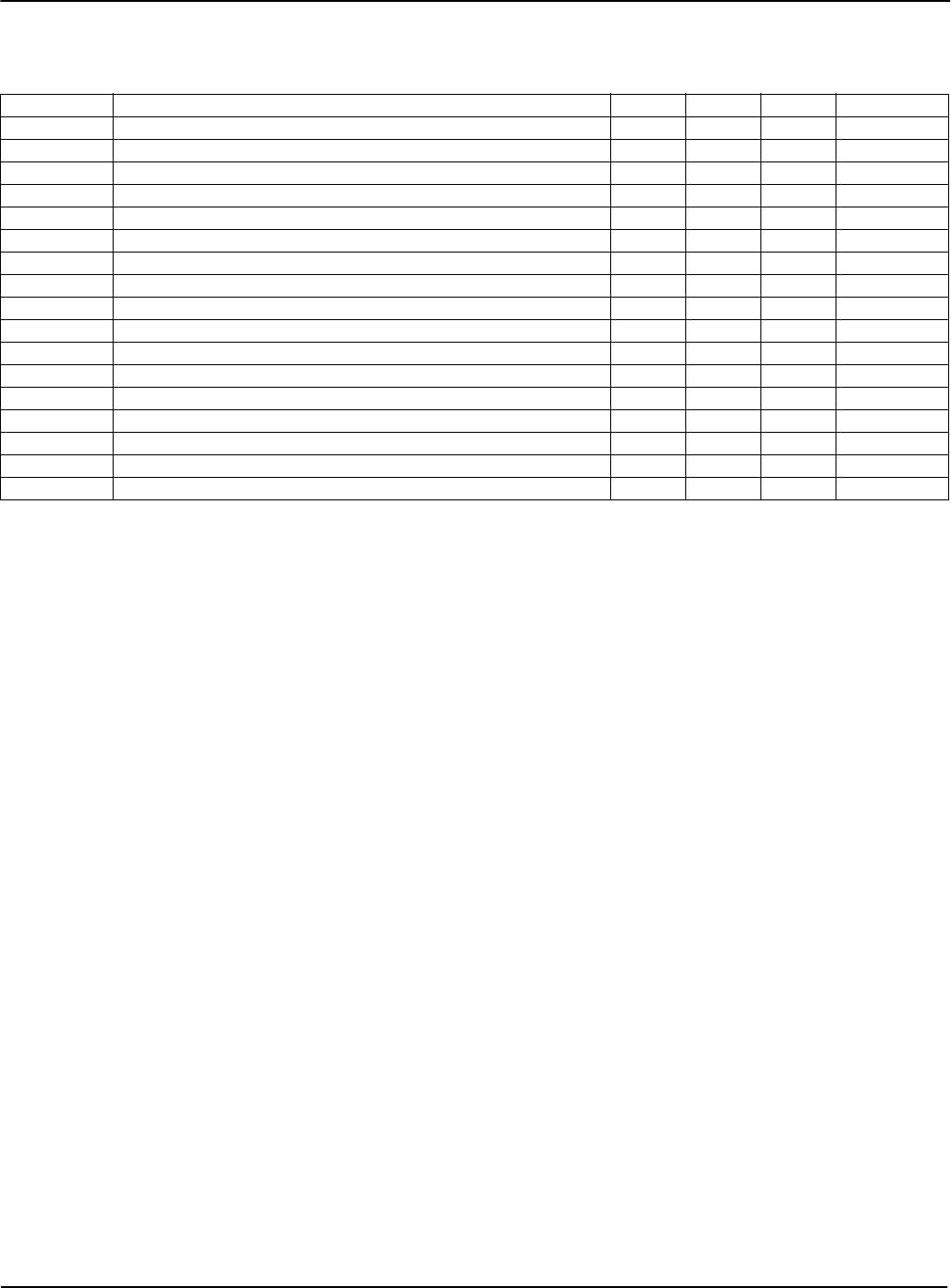

Table 6-33: 320x240 Epson D-TFD Panel Horizontal Timing

Symbol Parameter Min Typ Max Units

t1

FPLINE pulse width 9 Ts (note 1)

t2

FPLINE falling edge to FPSHIFT start position 8.5 Ts

t3

FPSHIFT active period 331 Ts

t4

FPSHIFT start to first data 6 Ts

t5

Horizontal display period 320 Ts

t6 Last data to FPSHIFT inactive 5 Ts

t7

FPLINE falling edge to GPIO4 first pulse falling edge 1 Ts

t8

Horizontal total period 400 Ts

t9 GPIO4 first pulse falling edge to second pulse falling edge 200 Ts

t10 GPIO4 pulse width 11 Ts

t11 GPIO1 pulse width 100 Ts

t12 GPIO1 low period 100 Ts

t13 GPIO0 pulse width 200 Ts

t14 GPIO6 low pulse width 90 Ts

t15 GPIO6 rising edge to GPIO0 falling edge 10 Ts

t16 GPIO2 toggle to GPIO3 toggle 1 Ts

t17 GPIO5 low pulse width 7 Ts