Epson Research and Development Page 57

Vancouver Design Center

Hardware Functional Specification S1D13708

Issue Date: 02/03/07 X39A-A-001-02

1. t8 is the delay from when data is placed on the bus until the data is latched into the write buffer.

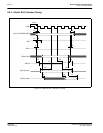

Table 6-11: Motorola REDCAP2 Interface Timing

Symbol Parameter Min Max Units

f

CLK

Bus Clock frequency

17 MHz

T

CLK

Bus Clock period

1/f

CLK

ns

t3

A[16:0], M/R#, R/W

, CSn setup to CLK rising edge

1ns

t4

A[16:0], M/R#, R/W

, CSn hold from CLK rising edge

0ns

t5a

CSn

asserted for MCLK = BCLK

8T

CLK

t5b

CSn

asserted for MCLK = BCLK ÷ 2

10 T

CLK

t5c

CSn

asserted for MCLK = BCLK ÷ 3

13 T

CLK

t5d

CSn

asserted for MCLK = BCLK ÷ 4

15 T

CLK

t6

EB0

, EB1 asserted to CLK rising edge (write cycle)

2ns

t7

EB0

, EB1 de-asserted to CLK rising edge (write cycle)

3ns

t8

D[15:0] input setup to 3rd CLK rising edge after EB0

or EB1 asserted low

(write cycle) (see note 1)

1ns

t9

D[15:0] input hold from 3rd CLK rising edge after EB0

or EB1 asserted low

(write cycle)

1ns

t10

OE

, EB0, EB1 setup to CLK rising edge (read cycle)

1ns

t11

OE

, EB0, EB1 hold to CLK rising edge (read cycle)

1ns

t12

D[15:0] output delay from OE

, EB0, EB1 falling edge

(read cycle)

511ns

t13a

1st CLK rising edge after EB0

or EB1 asserted low to D[15:0] valid for MCLK

= BCLK (read cycle)

5CLK + 16 ns

t13b

1st CLK rising edge after EB0

or EB1 asserted low to D[15:0] valid for MCLK

= BCLK ÷ 2 (read cycle)

8CLK + 16 ns

t13c

1st CLK rising edge after EB0

or EB1 asserted low to D[15:0] valid for MCLK

= BCLK ÷ 3 (read cycle)

9CLK + 16 ns

t13d

1st CLK rising edge after EB0

or EB1 asserted low to D[15:0] valid for MCLK

= BCLK ÷ 4 (read cycle)

11CLK + 16 ns

t14

CLK rising edge to D[15:0] output in Hi-Z (read cycle)

39ns