Epson Research and Development Page 115

Vancouver Design Center

Hardware Functional Specification S1D13708

Issue Date: 02/03/07 X39A-A-001-02

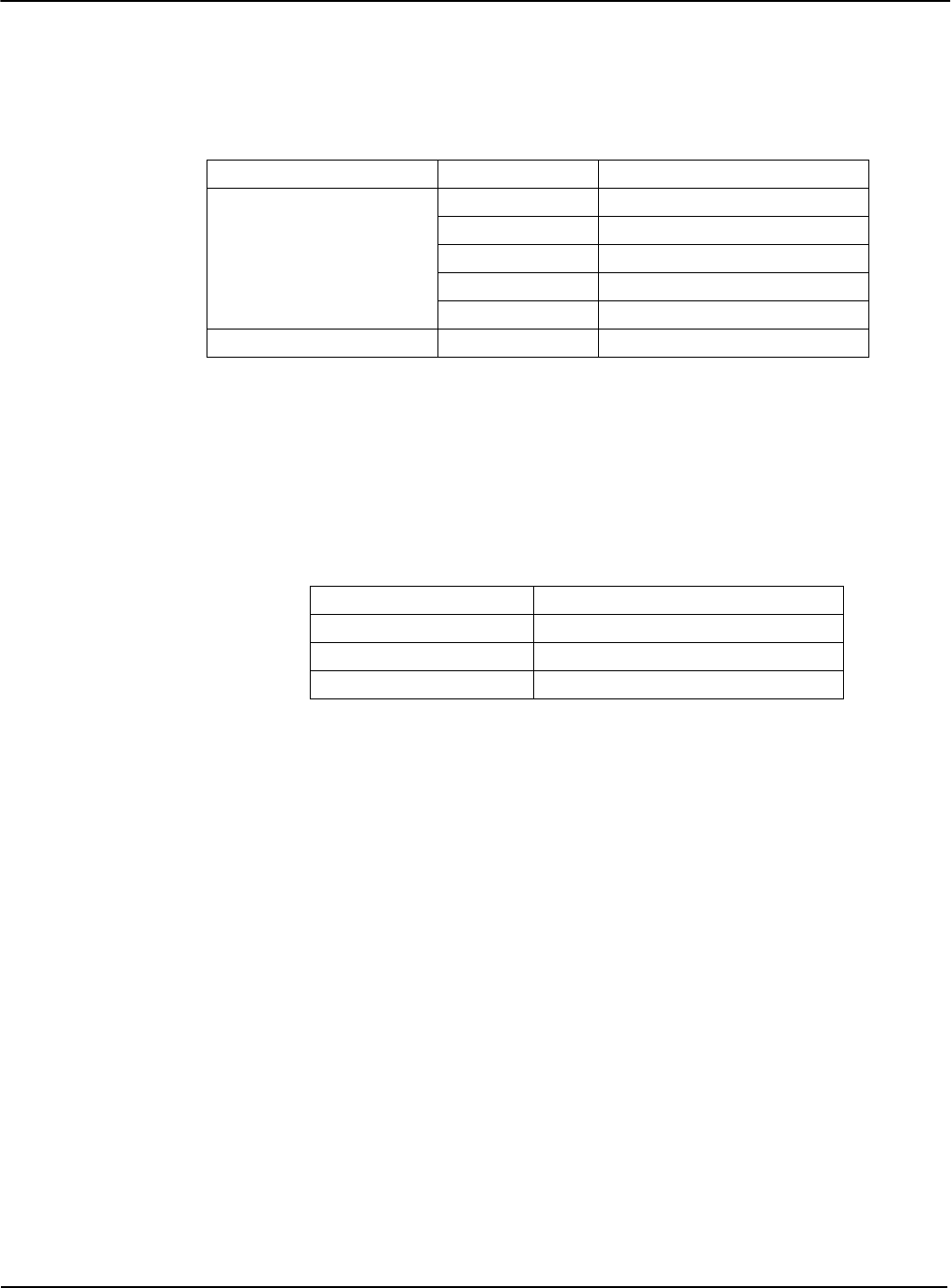

There is a relationship between the frequency of MCLK and PCLK that must be

maintained.

7.1.4 PWMCLK

PWMCLK is the internal clock used by the Pulse Width Modulator for output to the panel.

The source clock options for PWMCLK may be selected as in the following table.

For further information on controlling PWMCLK, see Section 8.3.9, “Pulse Width

Modulation (PWM) Clock and Contrast Voltage (CV) Pulse Configuration Registers” on

page 150.

Note

The S1D13708 provides Pulse Width Modulation output on the pin PWMOUT.

PWMOUT can be used to control LCD panels which support PWM control of the back-

light inverter.

Table 7-4: Relationship between MCLK and PCLK

SwivelView Orientation Color Depth (bpp) MCLK to PCLK Relationship

SwivelView 0° and 180°

16 f

MCLK

≥ f

PCLK

8f

MCLK

≥ f

PCLK

÷

2

4f

MCLK

≥ f

PCLK

÷

4

2f

MCLK

≥ f

PCLK

÷

8

1f

MCLK

≥ f

PCLK

÷

16

SwivelView 90° and 270° 16/8/4/2/1 f

MCLK

≥ 1.25f

PCLK

Table 7-5: PWMCLK Clock Selection

Source Clock Options PWMCLK Selection

CLKI REG[B1h] bit 0 = 0

CLKI2 REG[CAh] bit 1 = 0, REG[B1h] bit 0 = 1

XTAL REG[CAh] bit 1 = 1, REG[B1h] bit 0 = 1