Page 108 Epson Research and Development

Vancouver Design Center

S1D13708 Hardware Functional Specification

X39A-A-001-02 Issue Date: 02/03/07

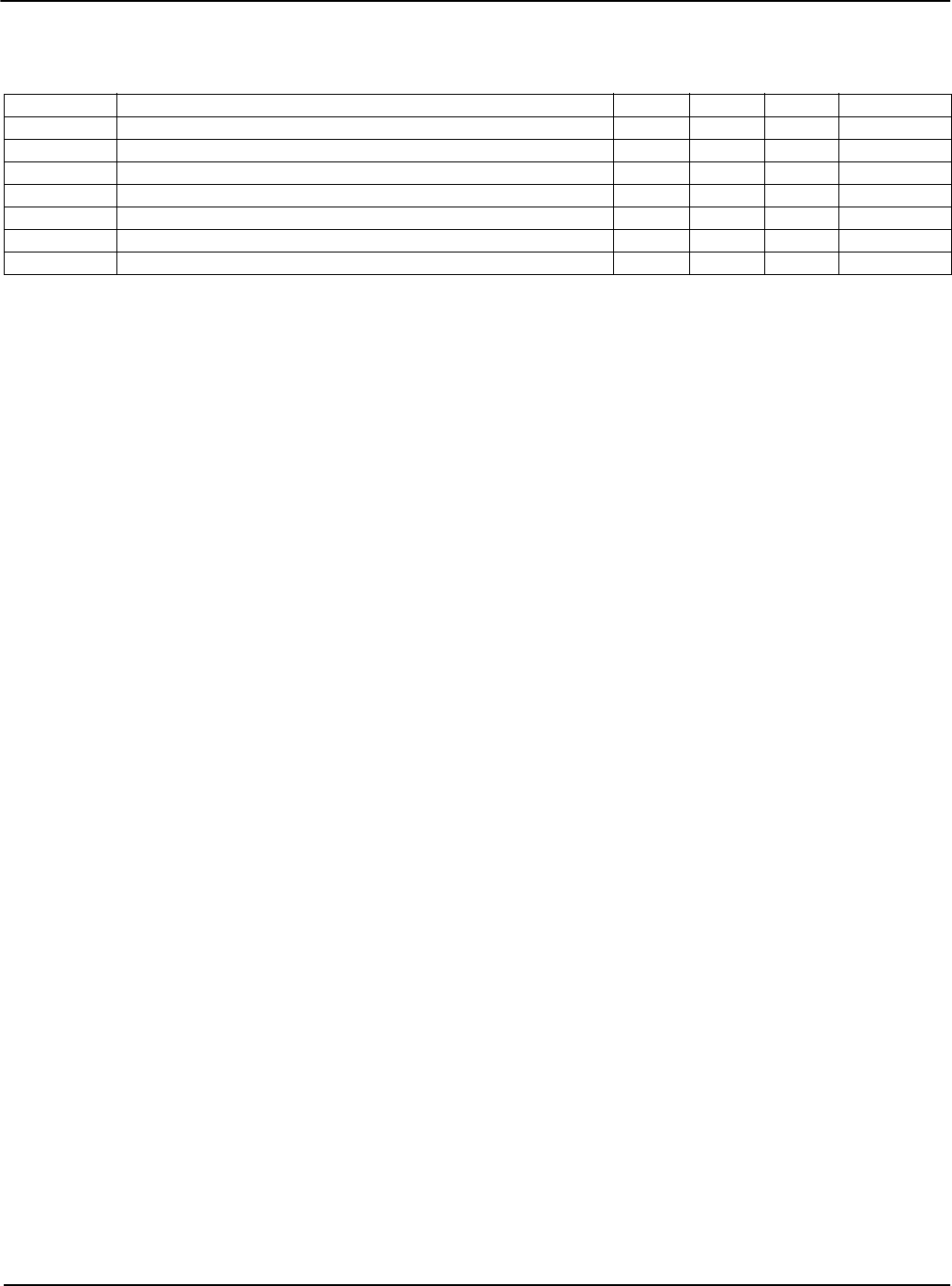

1. Ts = pixel clock period

2. t4typ = (REG[1Fh] bits 1-0, REG[1Eh] bits 7-0)

3. t5typ = (REG[1Dh] bits 1-0, REG[1Ch] bits 7-0) + 1

4. t6typ = ((REG[DAh] bits 7-0) x 2

5. t7typ = ((REG[DBh] bits 7-0) x 2

Note

When REG[DAh] = 0, GPIO5 (XOEV) stays HIGH.

Table 6-39: TFT Type 3 Vertical Timing

Symbol Parameter Min Typ Max Units

t1

Vertical total period 1 1024 Lines

t2

FPFRAME pulse width 1 Lines

t3

GPIO0 rising edge to FPFRAME rising (falling) edge 0.5 Lines

t4 Vertical display start position 1 note 2 Lines

t5

Vertical display period 1 note 3 1024 Lines

t6

GPIO5 rising edge to GPIO0 rising edge 0 note 4 512 Ts

t7 GPIO0 rising edge to GPIO5 falling edge 0 note 5 512 Ts