Page 84 Epson Research and Development

Vancouver Design Center

S1D13708 Hardware Functional Specification

X39A-A-001-02 Issue Date: 02/03/07

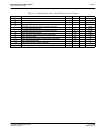

6.4.8 Generic TFT Panel Timing

Figure 6-29 Generic TFT Panel Timing

VT = Vertical Total = [(REG[19h] bits 1-0, REG[18h] bits 7-0) + 1] lines

VPS = FPFRAME Pulse Start Position = (REG[27h] bits 1-0, REG[26h] bits 7-0) lines

VPW = FPFRAME Pulse Width = [(REG[24h] bits 2-0) + 1] lines

VDPS = Vertical Display Period Start Position = (REG[1Fh] bits 1-0, REG[1Eh] bits 7-0) lines

VDP = Vertical Display Period = [(REG[1Dh] bits 1-0, REG[1Ch] bits 7-0) + 1] lines

HT = Horizontal Total = [((REG[12h] bits 6-0) + 1) x 8] pixels

HPS = FPLINE Pulse Start Position = [(REG[23h] bits 1-0, REG[22h] bits 7-0) + 1] pixels

HPW = FPLINE Pulse Width = [(REG[20h] bits 6-0) + 1] pixels

HDPS = Horizontal Display Period Start Position= [(REG[17h] bits 1-0, REG[16h] bits 7-0) + 5] pixels

HDP = Horizontal Display Period = [((REG[14h] bits 6-0) + 1) x 8] pixels

*For TFT panels, the HDP must be a minimum of 16 pixels and must be increased by multiples of 8.

*Panel Type Bits (REG[10h] bits 1-0) = 01 (TFT)

*FPLINE Pulse Polarity Bit (REG[20h] bit 7) = 0 (active low)

*FPFRAME Polarity Bit (REG[24h] bit 7) = 0 (active low)

FPFRAME

VT (= 1 Frame)

DRDY

FPLINE

DRDY

FPLINE

VDPS

VPS

VPW

VDP

HT (= 1 Line)

HPS

HDPS HDP

FPDAT[17:0]

FPDAT[17:0]

invalid invalid

FPSHIFT

HPW